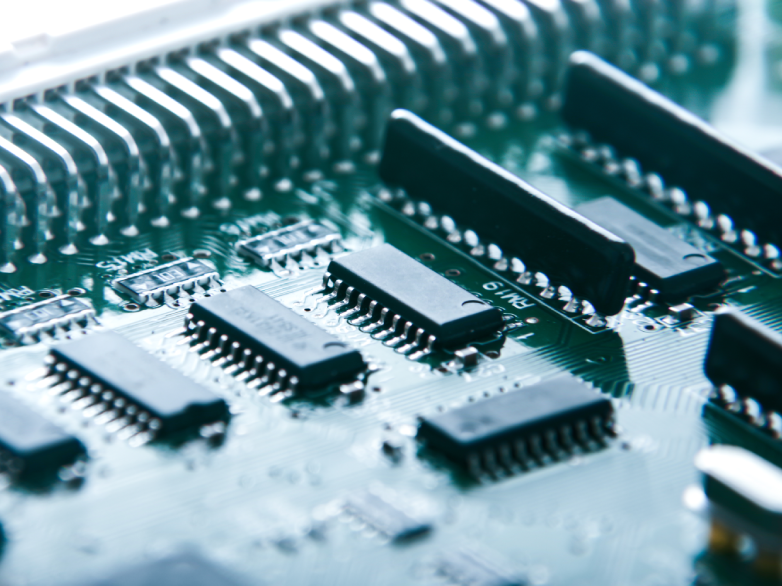

Front End Design

We specialize in translating ASIC functional specification into microarchitecture and RTL using appropriate blend of high-performance IP/SoC design techniques.

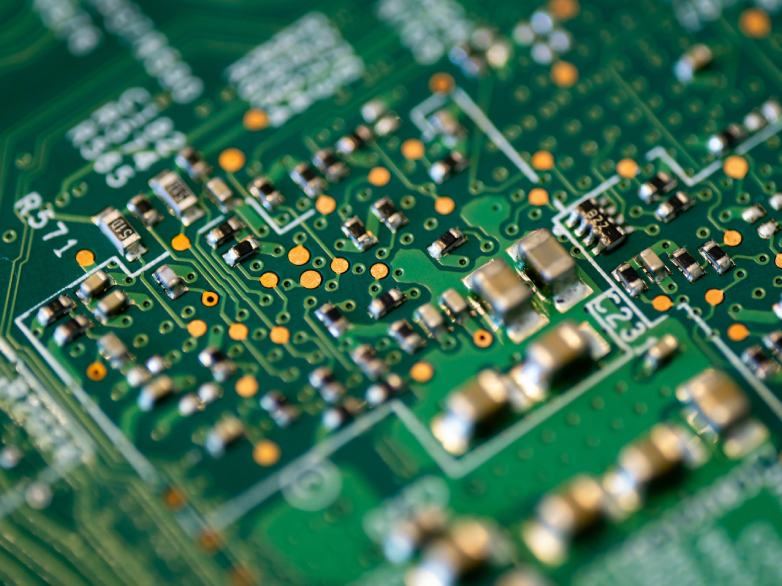

Physical Design

Wide and deep expertise in all areas of Physical Design from synthesis to GDSII. This also includes STA closure, power implementation, bump planning etc. We take pride in our special, custom recipes that help enhance performance, reduce TAT of design cycle, enhance QOR and optimize power and area.

Design Verification

Our team excels in delivering comprehensive design verification services including UPF, UVM & CCD methodologies, guarantying complete functional and code coverage.

Low Power Solutions

We drive low-power techniques and solutions such as UPF, voltage island, multi-VT, clock gating, power gating etc that optimize energy efficiency without compromising performance.

Design for Test

We specialize in incorporating and simulating cutting-edge Design for Testability (DFT) features, including SCAN, Compression, MBIST, BISR, BSCAN etc. for hierarchical designs and IPs, that guaranties silicon integrity.

Design Automation

Our team of engineers are experts in creating Custom Design Flows, Design Automation solutions and Visualizations using latest software technologies, which helps engineering teams reduce their TAT throughout the design cycle and enhances efficiency of project management.

10+ /Years

- Years of Leadership Experience

100+ /Designs

- Taped Out By Leadership Team

<10nm /SOCs

- Multiple Complex SOCs Delivered

Embedded Systems

Embedded OS & BSP Development

BSPs with minimal modifications on similar target boards Deep experience in BSP porting services BSP development with low-level operating system code and device driver code Full BSP including boot loaders (U-Boot)

IIoT Product Design & Development

Designed and Developed Industrial IOT products (Remote Monitoring Devices) IOT devices based on FreeRTOS, Linux OS Monitoring environmental data, physical data using variety of sensors data Design and integration of sensors and hardware modules Post - Silicon Validation Expertise in Post-silicon validation for with CMSIS standard device driver Below are four types of post-silicon tests done Functional bug hunting Random instruction testing Memory subsystem validation I/O concurrency

Post - Silicon Validation

Expertise in Post-silicon validation for with CMSIS standard device driver Below are four types of post-silicon tests done Functional bug hunting Random instruction testing Memory subsystem validation I/O concurrency

Diagnostic Software Development

Expert in diagnostic firmware design, development and testing for Ethernet IP Switches, Routers Expert in board bring up including devices like SoC, ASIC, PHY on board Design and Development of functional tests(diagnostic) for Ethernet IP Switch

Pre - Silicon Validation

Specializes in Pre Silicon Validation for PCIE Gen5 IP with Xilinx FPGA platform Specializes in Pre Silicon Validation for CXL 1.1 / 2.0 /3.0 IP with Xilinx FPGA Platform Expert in PCIE CV, CXL CV Testing

Firmware and Device Driver Development

Developing MCU firmware, Bare metal Device Drivers Designing System Architecture and Partitioning Creating Hardware Abstraction Layer (HAL) Building Protocol Stack Experience in CPU architectures such as ARM, PowerPC, AVR, and PIC

Our Community Commitment Includes Establishing A Flagship Initiative

Useful Links

©aquilabusinesssolutions 2025 | All Rights Reserved | Designed by Mercury Softech